計(jì)算機(jī)的硬件結(jié)構(gòu)是現(xiàn)代信息技術(shù)的基石,它不僅是理解計(jì)算機(jī)工作原理的起點(diǎn),更是驅(qū)動(dòng)技術(shù)創(chuàng)新的核心。從最基礎(chǔ)的認(rèn)識(shí)到深度的開發(fā)實(shí)踐,是一個(gè)從宏觀框架到微觀實(shí)現(xiàn)、從理論學(xué)習(xí)到工程應(yīng)用的系統(tǒng)性過程。

一、核心硬件結(jié)構(gòu):計(jì)算機(jī)的五大支柱

計(jì)算機(jī)硬件系統(tǒng)通常由五大核心部件構(gòu)成,它們協(xié)同工作,共同執(zhí)行計(jì)算、存儲(chǔ)和控制任務(wù)。

- 中央處理器(CPU):作為計(jì)算機(jī)的“大腦”,CPU負(fù)責(zé)解釋和執(zhí)行指令。其內(nèi)部結(jié)構(gòu)復(fù)雜,包括算術(shù)邏輯單元(ALU)、控制單元(CU)和寄存器組。理解CPU的指令集架構(gòu)(如x86、ARM)、多核技術(shù)、流水線和緩存層次結(jié)構(gòu)是硬件開發(fā)的底層知識(shí)。

- 存儲(chǔ)器系統(tǒng):這是一個(gè)層次化的存儲(chǔ)體系。從高速但容量小的CPU緩存、作為主存的內(nèi)存(RAM),到長期存儲(chǔ)數(shù)據(jù)的硬盤(HDD/SSD)和只讀存儲(chǔ)器(ROM)。開發(fā)中需要深刻理解它們之間的速度差異、尋址方式以及數(shù)據(jù)一致性問題。

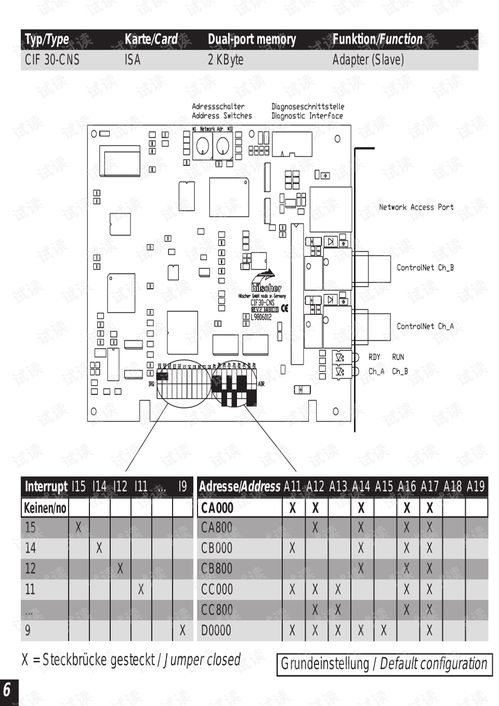

- 輸入/輸出(I/O)系統(tǒng):這是計(jì)算機(jī)與外界交互的橋梁,包括鍵盤、鼠標(biāo)、顯示器等外設(shè)及其控制器。硬件開發(fā)中,I/O端口的編程、中斷處理機(jī)制和直接內(nèi)存訪問(DMA)技術(shù)是關(guān)鍵。

- 主板與總線:主板是所有硬件的物理連接平臺(tái)。總線(如系統(tǒng)總線、I/O總線)是各部件間傳輸數(shù)據(jù)、地址和控制信號(hào)的“高速公路”。總線協(xié)議、帶寬和時(shí)序是硬件設(shè)計(jì)時(shí)必須嚴(yán)格遵循的規(guī)范。

- 電源與輔助系統(tǒng):為所有硬件提供穩(wěn)定、純凈的電力,并管理散熱,確保系統(tǒng)在最佳狀態(tài)下運(yùn)行。在開發(fā)高性能硬件時(shí),電源設(shè)計(jì)和熱管理是決定穩(wěn)定性的重要因素。

二、硬件開發(fā):從認(rèn)知到創(chuàng)造的躍遷

僅僅認(rèn)識(shí)這些部件是遠(yuǎn)遠(yuǎn)不夠的。硬件開發(fā)是將理論知識(shí)轉(zhuǎn)化為物理實(shí)體的工程實(shí)踐,它涉及多個(gè)層面的深度工作:

- 需求分析與架構(gòu)設(shè)計(jì):這是開發(fā)的第一步。需要明確硬件的功能、性能指標(biāo)(如算力、功耗、成本)和兼容性要求。在此基礎(chǔ)上,設(shè)計(jì)系統(tǒng)整體架構(gòu),確定CPU選型、內(nèi)存規(guī)格、I/O接口方案等,繪制出硬件系統(tǒng)的“藍(lán)圖”。

- 電路設(shè)計(jì)與仿真:使用電子設(shè)計(jì)自動(dòng)化(EDA)工具(如Cadence、Altium Designer)進(jìn)行原理圖設(shè)計(jì)和印刷電路板(PCB)布局。設(shè)計(jì)過程中,需要對(duì)信號(hào)完整性、電源完整性、電磁兼容性(EMC)進(jìn)行嚴(yán)謹(jǐn)?shù)姆治龊头抡妫_保電路在理論上可行且可靠。

- 核心邏輯設(shè)計(jì)與硬件描述語言(HDL):對(duì)于CPU、專用集成電路(ASIC)或現(xiàn)場(chǎng)可編程門陣列(FPGA)的開發(fā),需要使用Verilog或VHDL等硬件描述語言來定義數(shù)字邏輯電路的行為和結(jié)構(gòu)。這要求開發(fā)者具備深厚的數(shù)字電路和計(jì)算機(jī)體系結(jié)構(gòu)知識(shí)。

- 原型制造與測(cè)試:將設(shè)計(jì)文件交付制造,生產(chǎn)出PCB板,并焊接元器件,組裝成原型機(jī)。隨后進(jìn)入嚴(yán)格的測(cè)試階段,包括功能測(cè)試、性能壓力測(cè)試、環(huán)境可靠性測(cè)試等,通過調(diào)試發(fā)現(xiàn)并修復(fù)設(shè)計(jì)缺陷。

- 固件與驅(qū)動(dòng)程序開發(fā):硬件需要“靈魂”才能工作。這包括寫入到ROM中的基本輸入輸出系統(tǒng)(BIOS)或統(tǒng)一可擴(kuò)展固件接口(UEFI),以及操作系統(tǒng)級(jí)別的設(shè)備驅(qū)動(dòng)程序。它們是硬件與軟件溝通的翻譯官,其開發(fā)質(zhì)量直接影響硬件效能的發(fā)揮。

- 系統(tǒng)集成與驗(yàn)證:將開發(fā)好的硬件與操作系統(tǒng)、應(yīng)用軟件進(jìn)行整合,驗(yàn)證整個(gè)計(jì)算機(jī)系統(tǒng)是否滿足最初的設(shè)計(jì)目標(biāo)。這是一個(gè)跨學(xué)科的復(fù)雜過程,需要硬件工程師與軟件工程師緊密協(xié)作。

三、現(xiàn)代硬件開發(fā)的趨勢(shì)與挑戰(zhàn)

當(dāng)前,計(jì)算機(jī)硬件開發(fā)正朝著更集成、更智能、更專用的方向發(fā)展:

- 異構(gòu)計(jì)算:CPU不再是唯一的計(jì)算核心,圖形處理器(GPU)、神經(jīng)網(wǎng)絡(luò)處理器(NPU)、張量處理單元(TPU)等協(xié)同工作,針對(duì)特定任務(wù)(如圖形渲染、AI推理)進(jìn)行優(yōu)化。

- 片上系統(tǒng)(SoC):將CPU、GPU、內(nèi)存控制器、多種I/O接口等集成到單一芯片上,極大地提升了能效比和緊湊性,廣泛應(yīng)用于手機(jī)、物聯(lián)網(wǎng)設(shè)備。

- 開放架構(gòu)與RISC-V:RISC-V開源指令集的出現(xiàn),降低了處理器設(shè)計(jì)的門檻,激發(fā)了硬件創(chuàng)新的活力,使定制化CPU開發(fā)成為可能。

- 挑戰(zhàn):與此開發(fā)者面臨著摩爾定律放緩后的性能提升瓶頸、幾何級(jí)數(shù)增長的芯片設(shè)計(jì)成本、以及日益嚴(yán)峻的功耗和散熱問題。

###

“認(rèn)識(shí)計(jì)算機(jī)的硬件結(jié)構(gòu)”是邁入科技殿堂的第一步,而“計(jì)算機(jī)硬件開發(fā)”則是將創(chuàng)意與知識(shí)鍛造成現(xiàn)實(shí)生產(chǎn)力的深度旅程。它要求開發(fā)者不僅要有扎實(shí)的電子工程、計(jì)算機(jī)體系結(jié)構(gòu)基礎(chǔ),還要具備系統(tǒng)工程思維、嚴(yán)謹(jǐn)?shù)墓こ虒?shí)踐能力和持續(xù)學(xué)習(xí)新興技術(shù)的前瞻性。從理解一個(gè)現(xiàn)成系統(tǒng)的構(gòu)成,到親手創(chuàng)造一個(gè)全新的系統(tǒng),這正是硬件工程師從認(rèn)知者轉(zhuǎn)變?yōu)閯?chuàng)造者的非凡之路。